Processos de Build Atualmente Suportados:

Nota: A infraestrutura ainda está em fase de implementação, alguns processadores podem estar em estado de erro devido a problemas na configuração da infraestrutura.

| Name | Links | Extensions | XLEN | Language | Status | Full Log |

|---|---|---|---|---|---|---|

| RVX | Github | I | 32 | Verilog | Log | |

| Minerva | Github | Amaranth HDL(Python) | Log | |||

| mriscv | Github | 32 | Verilog | Log | ||

| e200_opensource | Github | Verilog | Log | |||

| serv | Github | I[M] | 32 | Verilog | Log | |

| biriscv | Github | 32 | Verilog | Log | ||

| picorv32 | Github | 32 | Verilog | Log | ||

| DarkRISCV | Github | E/I | 32 | Verilog | Log | |

| Tinyriscv | Github | IM | 32 | Verilog | Log | |

| Auk-V | Github | 32 | Verilog | Log | ||

| DV-CPU-RV | Github | 32 | Verilog | Log | ||

| NeoRV32-Verilog | Github | 32 | Verilog | Log | ||

| NeoRV32 | Github | 32 | VHDL | Log | ||

| Tethorax | Github | VHDL | Log | |||

| Baby Risco 5 | Github | E | 32 | Verilog | Log | |

| Pequeno Risco 5 | Github | I | 32 | Verilog | Log | |

| Risco 5 | Github | IM | 32 | Verilog | Log | |

| Grande Risco 5 | Github | IMBC_Zicsr | 32 | SystemVerilog | Log | |

| Nerv | Github | I | 32 | SystemVerilog | Log | |

| CV32e40p | Github | 32 | SystemVerilog | Log | ||

| Ibex (formerly Zero-riscy) | Github | EC IMC[B] | SystemVerilog | Log | ||

| CVA6 | Github | SystemVerilog | Log | |||

| Roa Logic RV12 | Github | I | 32 | SystemVerilog | Log | |

| SCR1 | Github | SystemVerilog | Log | |||

| ReonV | Github | 32 | VHDL | Log | ||

| SweRV EH1 | Github | SystemVerilog | Log | |||

| SweRV EL2 | Github | SystemVerilog | Log | |||

| SweRV EH2 | Github | SystemVerilog | Log | |||

| RPU | Github | IMZcsr | 32 | VHDL | Log | |

| RV01 | Github | VHDL | Log | |||

| Taiga | Github | SystemVerilog | Log | |||

| Maestro | Github | VHDL | Log | |||

| SSRV | Github | IMC | 32 | Verilog | Log | |

| RSD | Github | IMF | 32 | SystemVerilog | Log | |

| Kronos | Github | I_Zicsr_Zifencei | 32 | SystemVerilog | Log | |

| Klessydra-T03 | Github | [I/E][M][A] + Kless-Vect | 32 | VHDL-2008 | Log | |

| Klessydra-T02 | Github | I[A] | 32 | VHDL-2008 | Log | |

| Klessydra-F03 | Github | I[A] | 32 | VHDL-2008 | Log | |

| Klessydra-T13 | Github | I[A] | 32 | VHDL-2008 | Log | |

| Starsea_riscv | Github | Verilog | Log | |||

| NOEL-V | Github | GC | 32/64 | VHDL | Log | |

| RV3N | Github | Verilog | Log | |||

| RISCuinho | Github | I | 32 | Verilog | Log | |

| Riskow | Github | I | 32 | Verilog | Log | |

| Riscado-V | Github | I | 32 | Verilog | Log | |

| Vexriscv | Github | I[M][A][F[D]][C] | 32 | Chisel | Log | |

| WARP-V | Github | TL-Verilog | Log | |||

| VeeR EH1 RISC-V | Github | SystemVerilog | Log | |||

| VeeR EL2 RISC-V | Github | SystemVerilog | Log | |||

| VeeR EH2 RISC-V | Github | SystemVerilog | Log | |||

| cdl_hardware | Github | CDL | Log | |||

| mr1 | Github | Chisel | Log | |||

| rocket | Github | 32 | Chisel | Log | ||

| freedom | Github | 32/64 | Chisel | Log | ||

| BOOM | Github | 64 | Chisel | Log | ||

| e203 | Github | Verilog | Log | |||

| RS5 | Github | SystemVerilog | Log | |||

| Black Parrot | Github | SystemVerilog | Log | |||

| FabScalar | Github | Verilog | Log | |||

| MicroRV32 | Github | IMC | 32 | Chisel | Log | |

| Piccolo | Github | Verilog | Log | |||

| Flute | Github | BlueSpec | Log | |||

| Toooba | Github | Verilog | Log | |||

| RISC-V core (ultraembedded) | Github | Verilog | Log | |||

| XiangShan | Github | Chisel | Log | |||

| Hazard3 | Github | 32 | Verilog | Log | ||

| NutShell | Github | GC | 32/64 | Chisel | Log | |

| Lizard | Github | IM | 64 | PyMTL | Log | |

| RiscyOO | Github | G | 64 | BlueSpec | Log | |

| MYTH Cores | Github | TL-Verilog | Log | |||

| Anfield/Balotelli | Github | IM | 64 | Verilog | Log | |

| I2SRV32-S-v1 | Github | 32 | Verilog | Log | ||

| I2SRV64-SS-v1 | Github | GC | 64 | Verilog | Log | |

| Leaf | Github | I | 32 | VHDL | Log | |

| AIRisc | Github | I[/E[M][C] Zocsr Zicntr | 32 | Verilog | Log | |

| CV32e41p | Github | IM[F][Zfinx]C[Zce] | 32 | SystemVerilog | Log | |

| CVE2 | Github | IMC/EMC | 32 | SystemVerilog | Log | |

| CV32E40S | Github | I/E[M][Zmmul] | 32 | SystemVerilog | Log | |

| CV32E40X | Github | 32 | SystemVerilog | Log | ||

| CVA5 | Github | IMD | 32 | SystemVerilog | Log | |

| Fedar F1 | Github | IM | 64 | Verilog | Log | |

| Harv | Github | I | 32 | VHDL | Log | |

| Hornet | Github | IM | 32 | Verilog | Log | |

| SprintRV | Github | IMZicsr | 32 | Verilog | Log | |

| mmRISC-1 | Github | IMAFC | 32 | Verilog | Log | |

| Openpiton | Github | 64 | Verilog | Log | ||

| Paranut | Github | SystemC | Log | |||

| Pulpino | Github | 32 | SystemVerilog | Log | ||

| Rift2Core | Github | GC | 64 | Chisel | Log | |

| RiftCore | Github | IMC | 64 | Verilog | Log | |

| Riscv Atom | Github | IC_Zicsr | 32 | Verilog | Log | |

| RV32IC-CPU | Github | IC | 32 | Verilog | Log | |

| Simodense | Github | Verilog | Log | |||

| SparrowRV | Github | IMZicsr | 32 | Verilog | Log | |

| arRISCado | Github | IMAC | 32 | Verilog | Log | |

| Kant-V | Github | I | 32 | Verilog | Log | |

| Mor1kx | Github | 32/64 | Verilog | Log | ||

| openc910 | Github | GCV | 64 | Verilog | Log | |

| Potato | Github | I | 32 | VHDL | Log | |

| muntjac | Github | IMAC[F][D]_ZiCSR_Zifencei | 64 | SystemVerilog | Log | |

| zero-riscy | Github | IMC | 32 | SystemVerilog | Log |

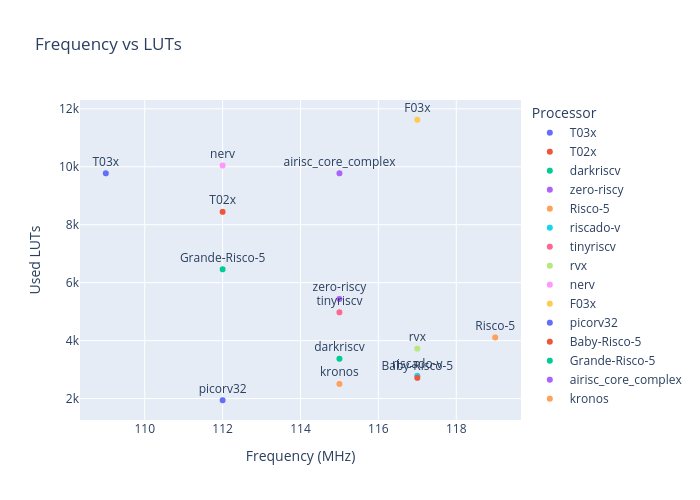

Frequência vs LUT4 na Placa FPGA Digilent Arty A7