#### A 130nm 32-bit RISC-V microcontroller

### Who we are

FPGA Programmers PCB makers

Hungry-learn students Learning and research environment

**Enthusiasts**

**Academia**

Industry expertise

(Ph.D. students each 2+ yrs exp)

Proven-silicon Circuit-design skills

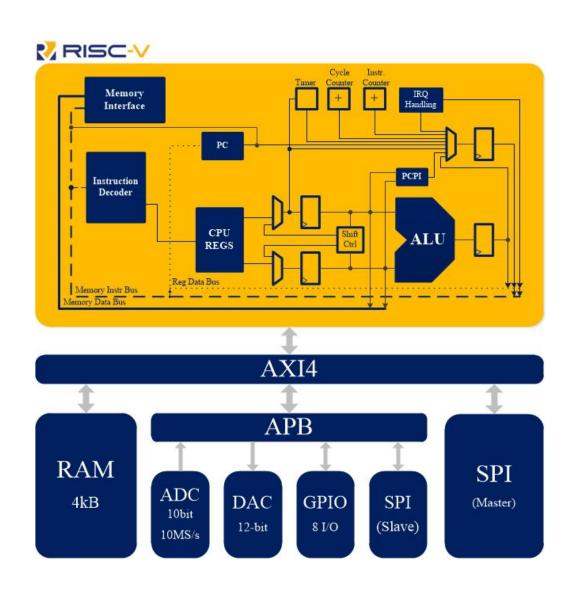

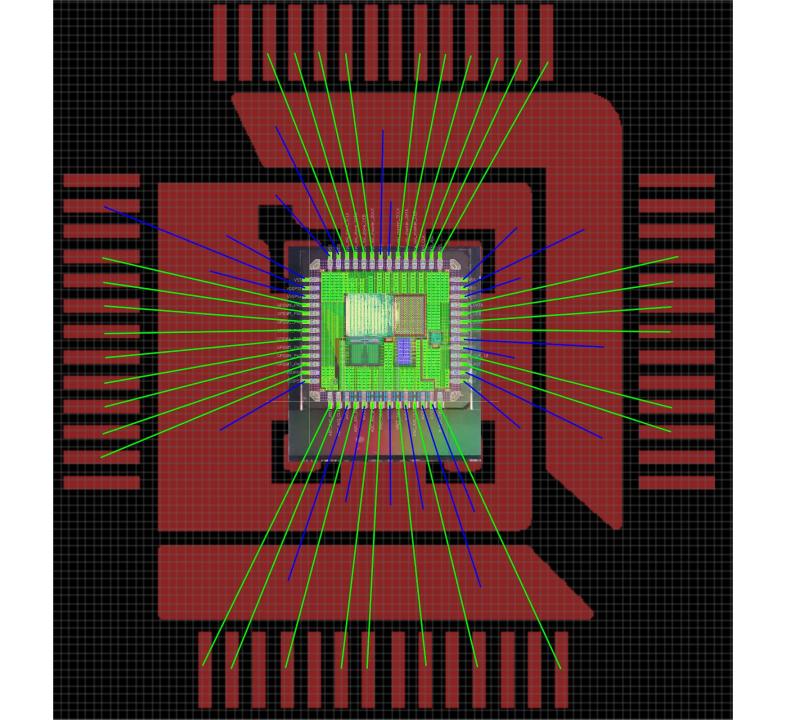

### A 32-bit RISC-V based microcontroller

#### Some more details

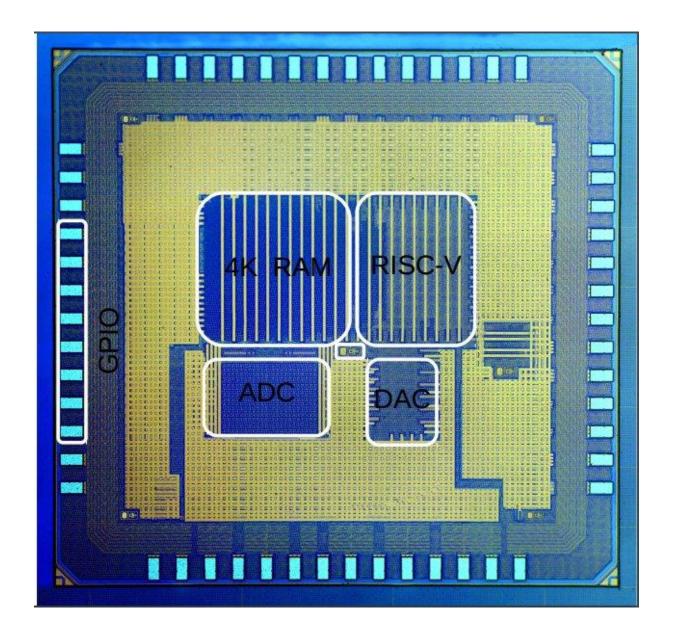

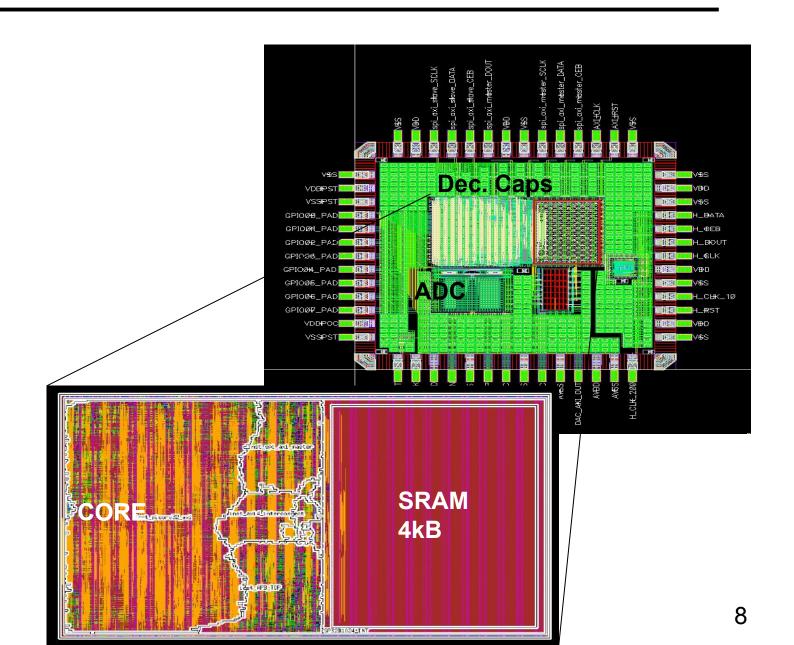

**TSMC 130nm GP**

I/O standard lib 2.5V

Regular VT cell lib

**□+Some crafted cells**

□Tested from 100kHz

to 200MHz

\_ <sub>□</sub>64 pins

**Core+interfaces area:**

**■800μm x 480μm**

| Pe | rfc     | rm          | an | ce |

|----|---------|-------------|----|----|

|    | ' I I 🔾 | / B   B   I |    |    |

μRISC-V

ISA RV32IM

Architecture Single-Issue In-Order 3-stage

TSMC 130nm GP Process

Die Area 2.1mm x 2.1mm

uP core area 0.12 mm<sup>2</sup>!

Max. Frequency 100MHz

1.2 V Core Voltage I/O Voltage 2.5V

Core Dynamic

Power

1.2V Current

@2.5MHz

$132 \mu W/MHz *$

1.8mA

| Clock Frequency [MHz]` | Total Current (1.2V and 2.5V supplies ) [mA] |  |  |

|------------------------|----------------------------------------------|--|--|

| 2.5                    | 2.5                                          |  |  |

| 5                      | 4.62                                         |  |  |

| 8.8                    | 5.01                                         |  |  |

| 10                     | 5.12                                         |  |  |

| 20                     | 6.13                                         |  |  |

| 40                     | 8.10                                         |  |  |

| 60                     | 10.20                                        |  |  |

| 80                     | 12.18                                        |  |  |

| 100                    | 14.13                                        |  |  |

| 120                    | 16.14                                        |  |  |

| 140                    | 18.09                                        |  |  |

| 160                    | 20.06                                        |  |  |

| 180                    | 21.89                                        |  |  |

| 200                    | 23.76                                        |  |  |

<sup>!</sup> Fully constrained clock and loads for SSLHH corner. Zero skew CTS.

<sup>\*</sup> Measured at 100MHz running three while loops.

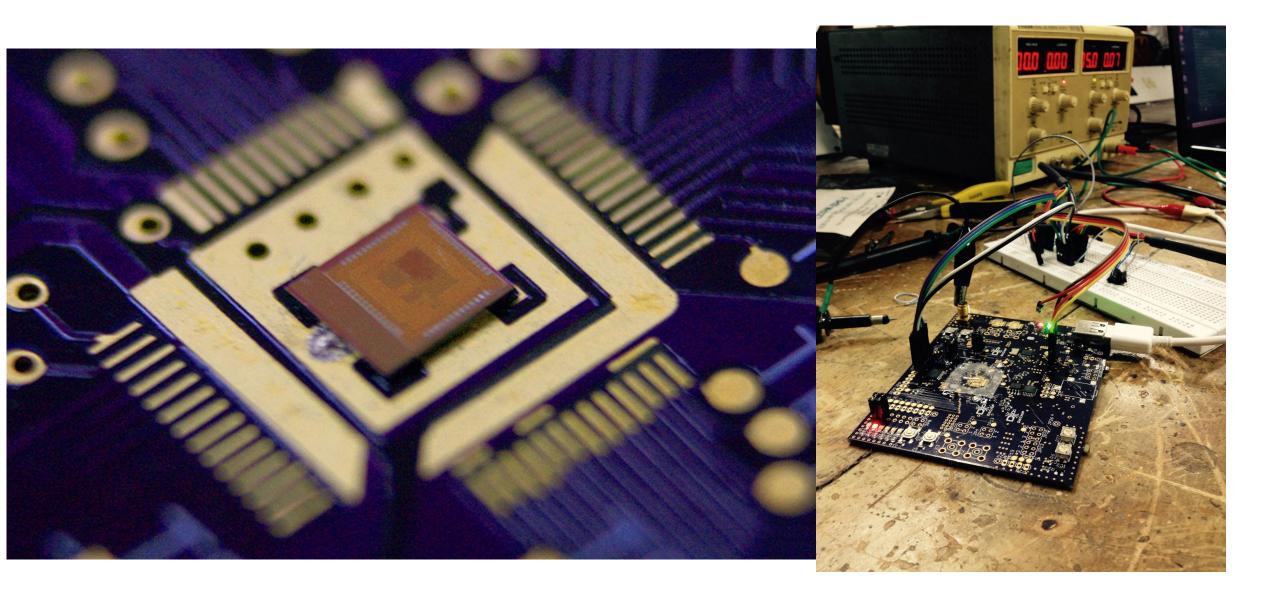

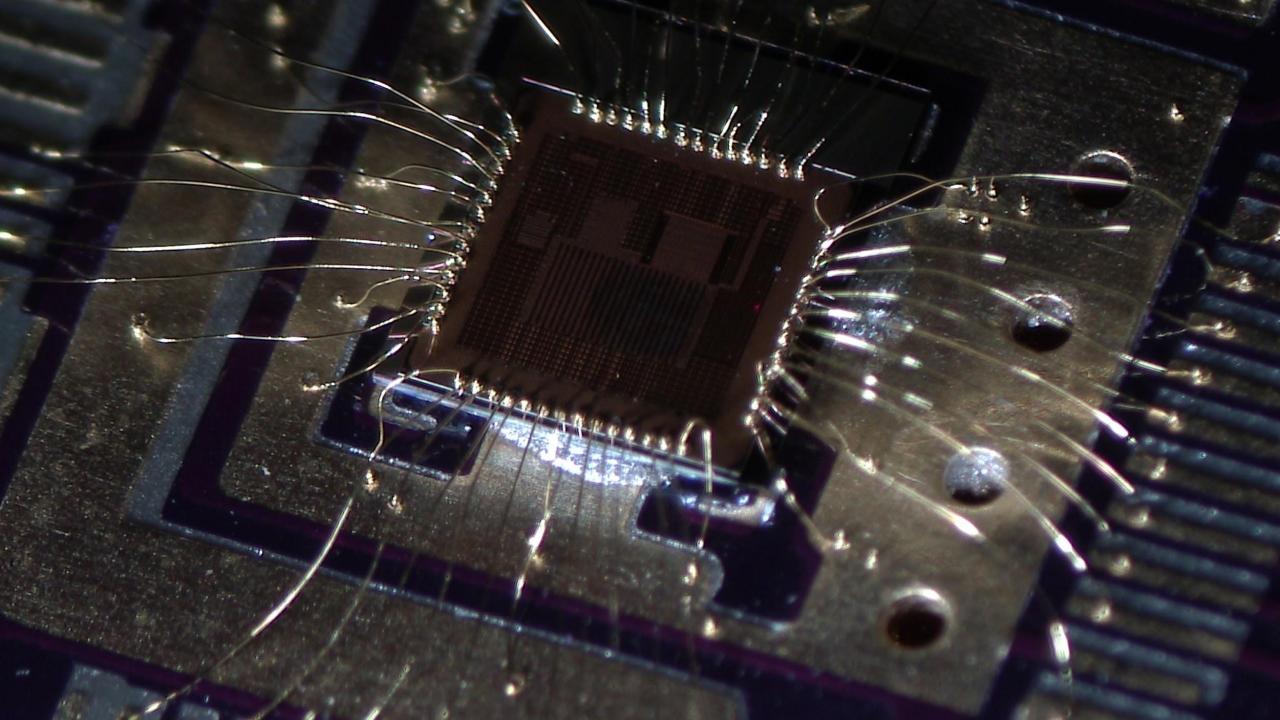

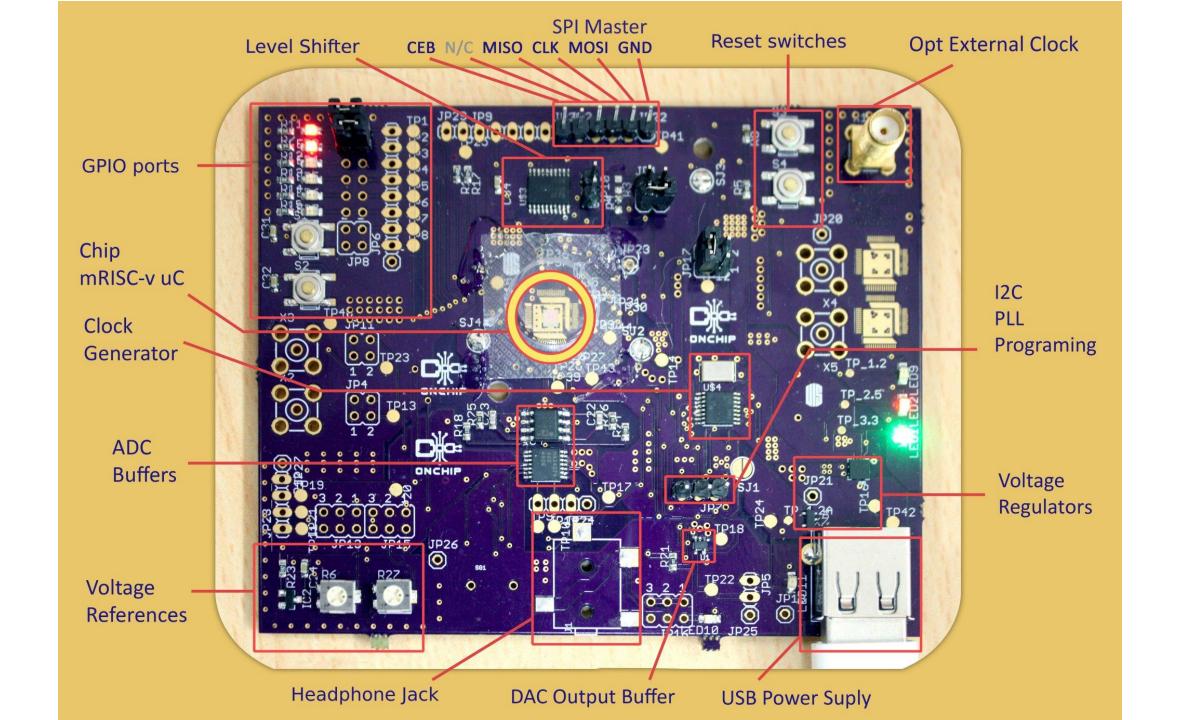

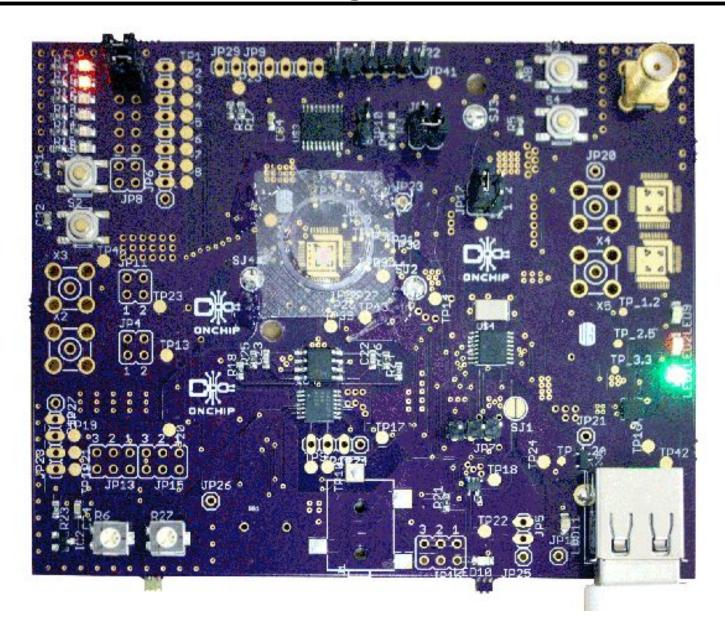

# Chip-on-board

### Give sth that has no bugs

## ATMEL SAMD21 ERRATA

Atmel

Atmel SAM D21E / SAM D21G / SAM D21J [DATASHEET] 1027

AtmeH42181K-SAM-D21\_Datasheet\_Complete-09/2016

3 – On pin PA24 and PA25 the pull-up and pull-down configuration is not disabled automatically when alternative pin function is enabled.

Errata reference: 12368

Fix/Workaround:

For pin PA24 and PA25, the GPIO pull-up and pull-down must be disabled before enabling alternative functions on them.

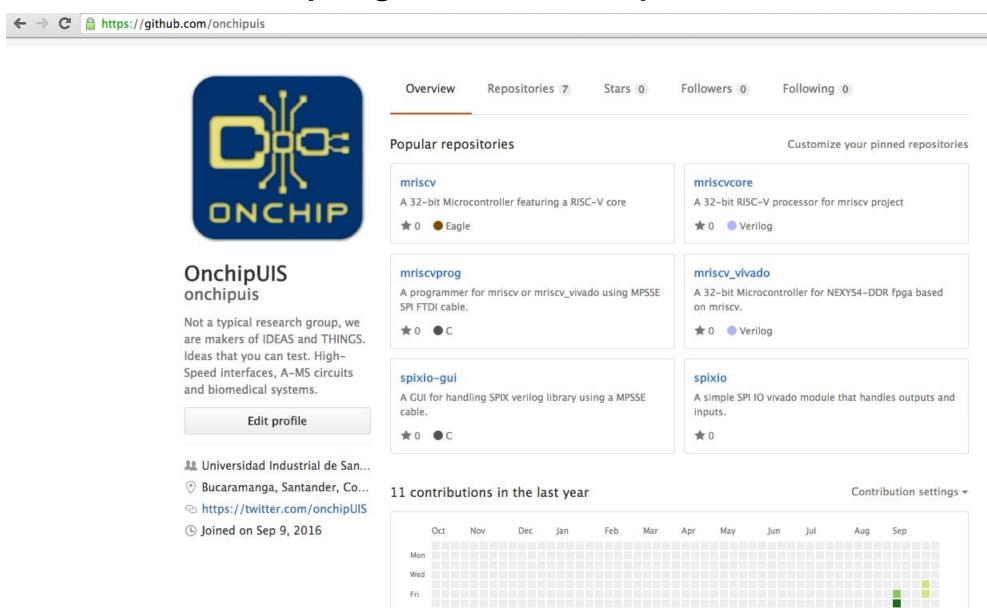

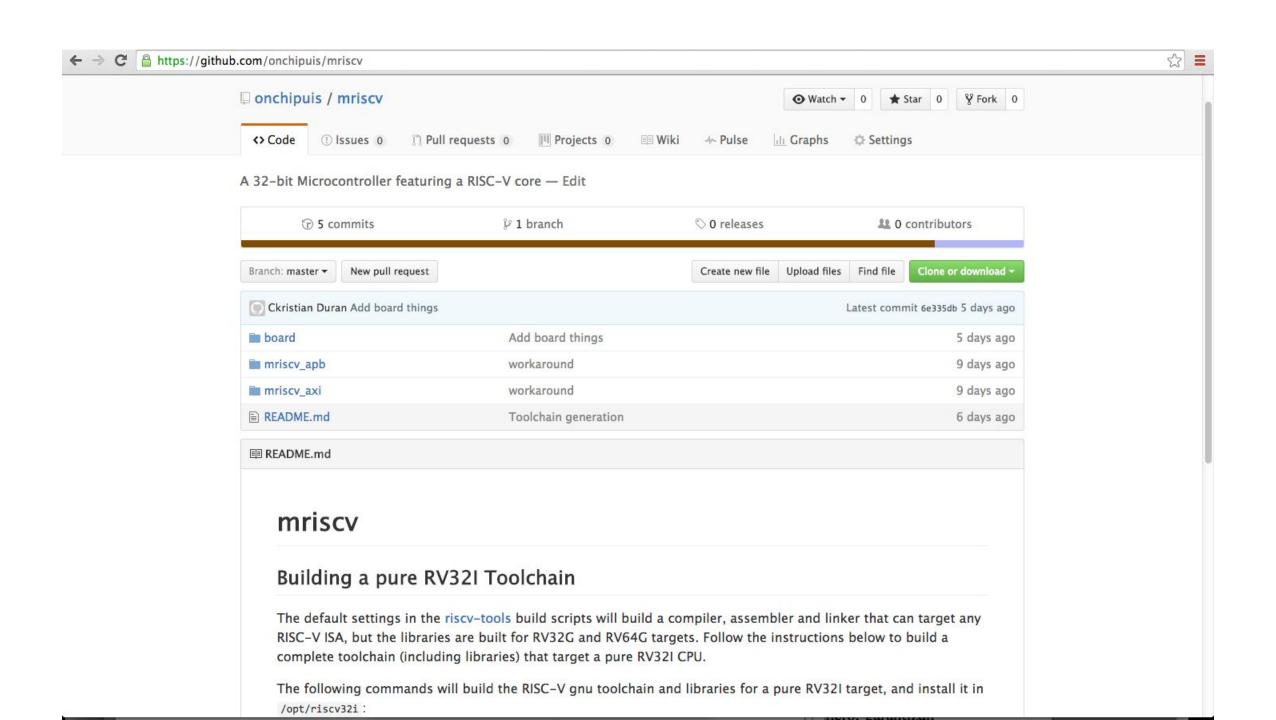

#### https://github.com/onchipuis

☆ =

Less More

Learn how we count contributions.

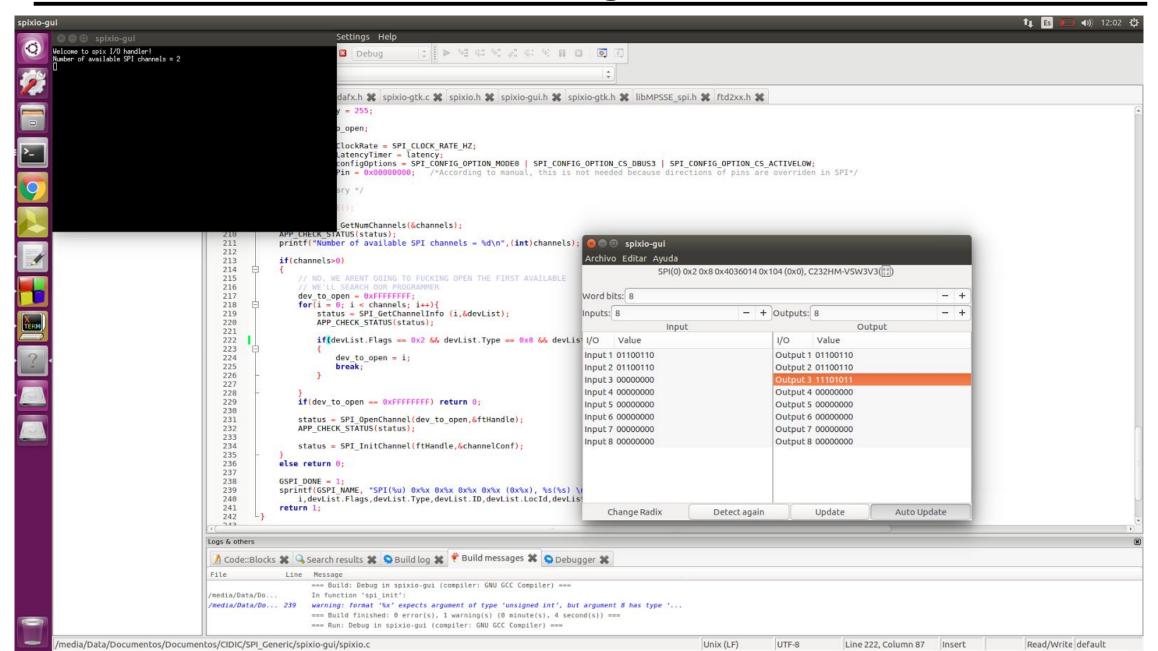

### **Tools for VLSI grad students**

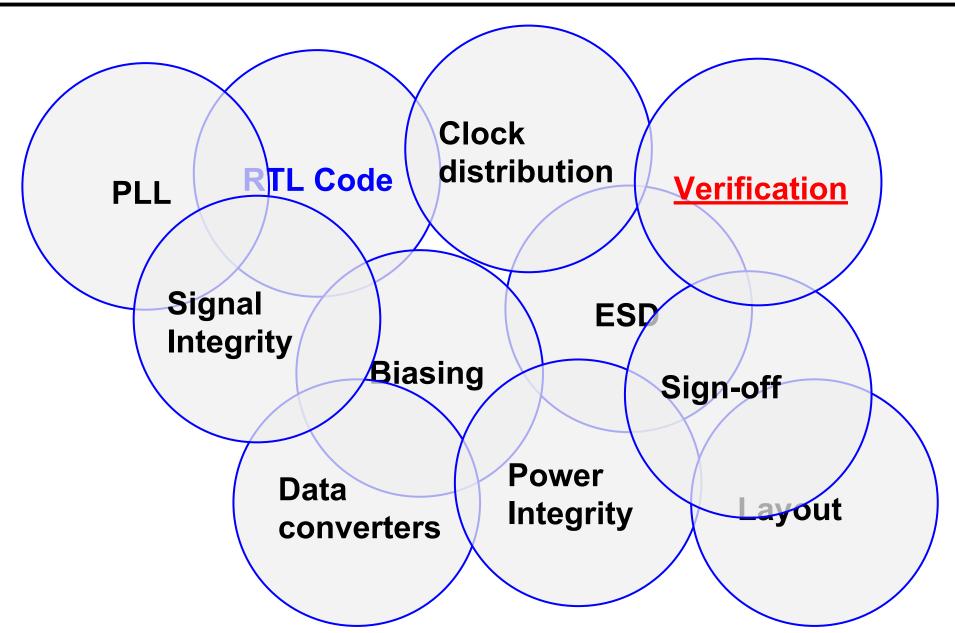

### Lot of circuits, lot of skills

# Diving into...

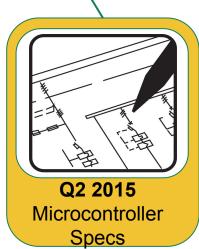

#### Some more details

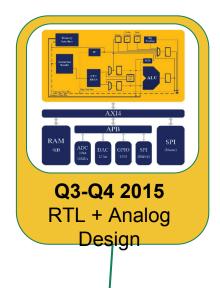

Q2 2016 Chip is back

Q4 2015 Tape Out

Q3 2016 Testing

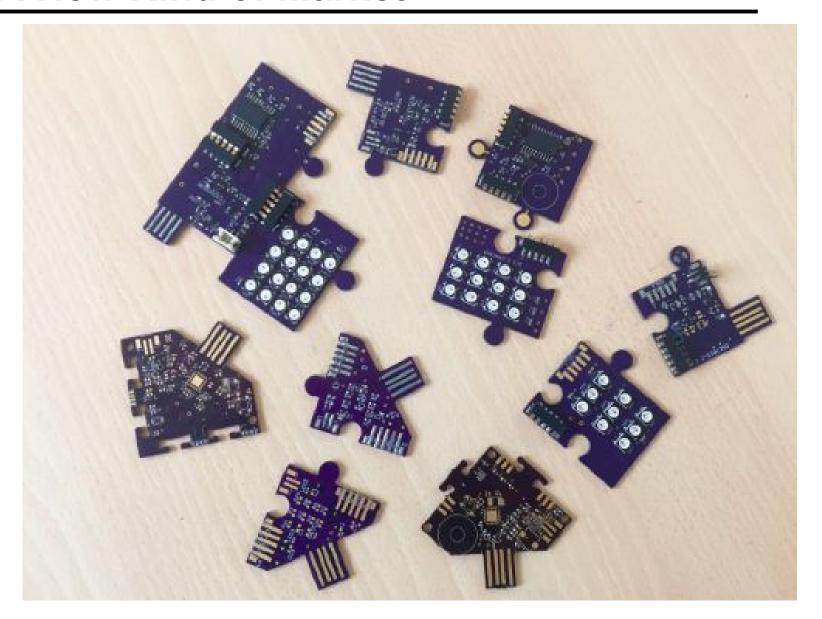

**Q2 2018**Puzzle Boards

### **A New Kind of Market**

Logo programming →

New programming model

### Thanks to:

- SAMPA Project

- ALICE-CERN

- Clifford Wolf

- RISC-V foundation

- Oshpark

- TPT

### What else we are doing:

- LPDDR3/LPDDR4 PCS + PMA

- USB 3.1 PCS + PMA (10Gb/s)

- LPDDR3/4 UVM VIP

- Circuits for Security: Lite key exchanging, TRNGs

- Research on CDR architectures

- Research on lite CNN

- Research on DFE + on-fly offset correction

New chip has just arrived!

### Funding is welcome

- Kickstarter microcontroller for a try to replace Atmel SAMD21? → \$350k for 70k packaged and tested chips, 2 revisions!

- Share MPW costs with more teams. Any school or private group want to team up?

- Foundries should start looking at these initiatives and fund "free" prototype silicon. High-level contacts are welcome.

- USB 2.0/3.1 PHY effort on indiegogo?

- Maybe RasberryPi or Arduino guys are willing to get some really open silicon?

#### **IDEAS ARE WELCOME**

## Demo before dinner, tonight!